사업영역

DIMM 검사기

반도체 조립 공정 진행 전 ,웨이퍼 상의 반도체 칩의 정상 작동 여부 테스트 및 Probe Card에 배치된 Probe Tip을 칩의 패드(pad)에 접촉시키고 , 주검사 장비로부터 전기 신호를 송신하여

칩의 정상유무 판독 테스트하는 기기 입니다.

칩의 정상유무 판독 테스트하는 기기 입니다.

-

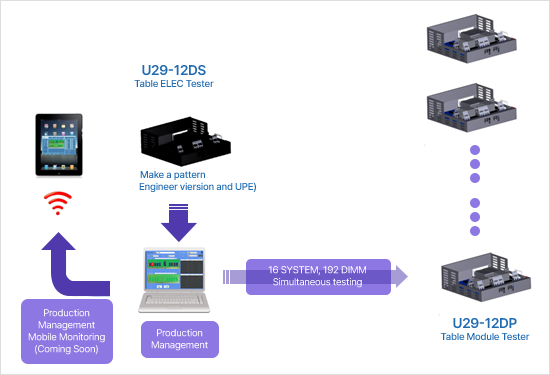

DIMM Module Testing Flow

DIMM Module Testing Flow -

Overview

Overview -

ANAL YSIS&SCRREN TESTER

ANAL YSIS&SCRREN TESTER

반도체 조립 공정 진행 전 ,웨이퍼 상의 반도체 칩의 정상 작동 여부 테스트 및 Probe Card에 배치된 Probe Tip을 칩의 패드(pad)에 접촉시키고 , 주검사 장비로부터 전기 신호를 송신하여

칩의 정상유무 판독 테스트하는 기기 입니다.

칩의 정상유무 판독 테스트하는 기기 입니다.

| Item | Specification |

|---|---|

| Parallel Test Para | Module 12Para(Extentionable) |

| Test Rane | Full Memory(By Bios testing) |

| Address Mode | Dream Device Operation(CS, Bank, Row, Col) |

| Address Depth | 18 Rows, 15 Columns, 4 Banks |

| Reset | DRAM Only Reset |

| Max. Frequency | DDR4 2933 |

| OVER CLOCK | MAX+15%(0.1Resolution) |

| Power Saving Mode | Power Down or Slef Refresh On/Off individually set as Test pattern |

| Data Sramble | On/Off |

| ECC Mode | On/off |

| (Date With Depth) | 72 IO per site |

| DDR4 Vdd | 0.5V~1.5V |

| CMD/ADD/DQS/DQ | 1 CLK(Option : 1/64 CLK) |

| Read/Write Gapless Mode | Unlimited time limit |

| Command Mode | 1N, 2N, 3N support simulataneously |

| AC Test(Clock 단위) | To Change In Register 0~Max Value |

| tRP, tRAS, tCWL, tCL, tRCD, tPRPDEN, tWTR, tCKE, tRTP, tWR, tRRD, tCCD, tODTOE, tXP, tXPOLL, tREFI, tXSDLL |

1/64 CLK support(Option) |

| Test Mode Test | possibility |

| Memory Training Test | possibility |

| Rand Margin Test | possibility |

| Self Refest Test | Max,600K/sec~infinit |

| Pattern Editor, Main UI Program, Data Log Analysis | |

| Software Program | Option : SHIMOO Program, Fail Bit Map, Pattern Conversion |

| Fail Triger | H/W or S/W |

| AC Power Supply | 110~240VAC, 50/60HZ Max. 10A for 110V; Max.5A for 220V |

| DC PARA | Impossibility or Option |